Building SIC-1 in VCB Part 4: Multiplexing clock

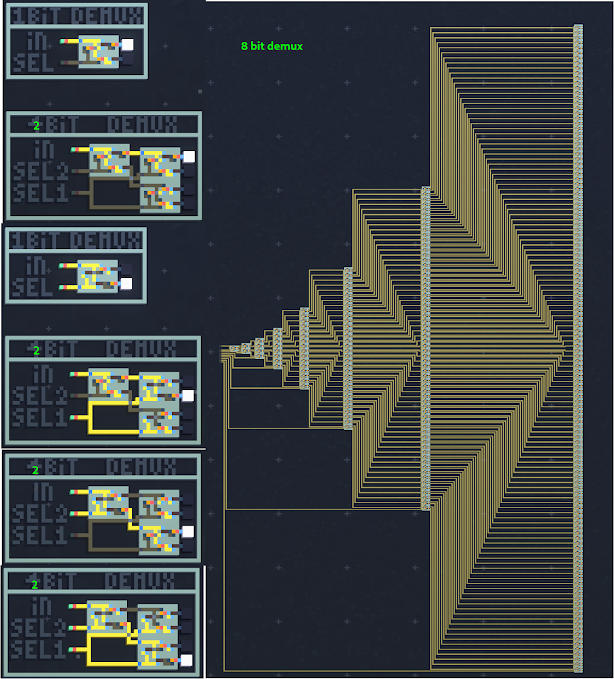

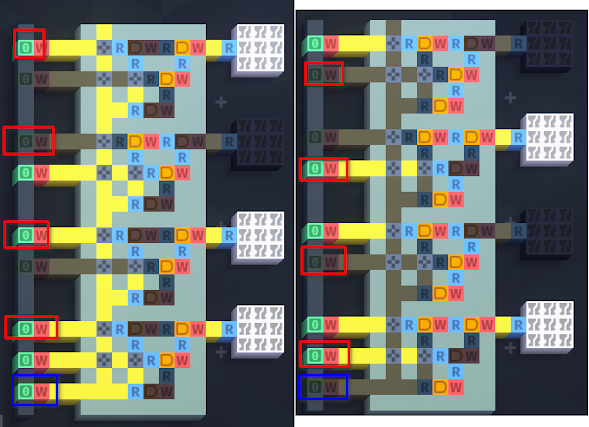

So, last time we built the RAM timing and full-adders, this time i found another important part that we're still missing The Multiplexer, or MUX, This circuit is sort of the opposite of the demuxer, where instead of turning an address into a selection of a RAM bank, we can switch between two signals. As you can see, the circuit has some very nice stacking behavior for the switching input (in blue) which lets us switch between a number of signals (selected in red) with just one input Of course we can also switch between multiple sets of input in a similar way to how we did with the demuxer, though here we get a rapidly shrinking set of data, and lots of inputs Of course, this way of looking at it is somewhat abstract, but it forms the basis for something i think most of us are familiar with but more generally, it allows us to "program" a sequence of outputs if instead of manually changing the selection pins, we attach this to a clock with a small counter circuit, Perhaps ...